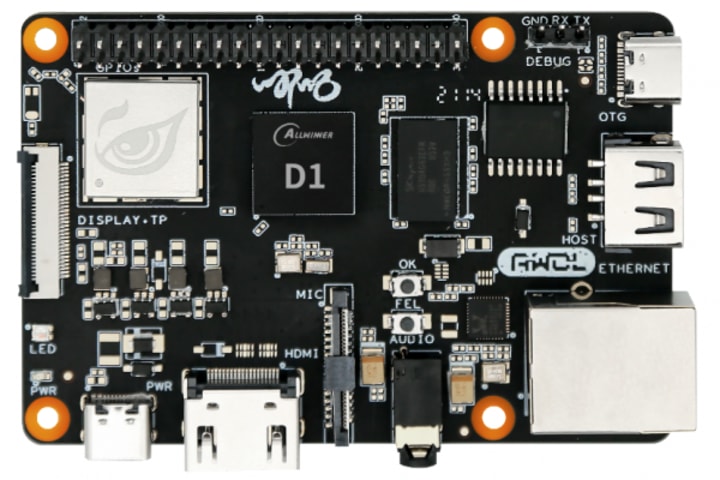

Canonical enables Ubuntu on Allwinner’s Nezha RISC-V boards

fter our previous announcement on the availability of Ubuntu running on RISC-V processors and hardware, we are proud to announce the Ubuntu release for additional RISC-V hardware – Allwinner’s Nezha board.

[...]

D1 is Allwinner’s first SoC based on the RISC-V ISA designed for multimedia decoding platforms. Running on Linux, RTOS and other systems, D1 integrates Alibaba T-Head’s 64-bit core and supports RVV and 1GHz frequency. At the same time, it supports up to 4K H.265/H.264 decoding, a built-in HiFi4 DSP, and an external connection of up to 2GB DDR3, which can be used in many fields such as smart cars, HMI, Smart home and education.

Nezha is an AIoT development board based on Allwinner’s D1 chip. It is the world’s first mass-produced development board that supports the 64-bit RISC-V instruction set and a Linux system.

Also: Linux Mint System Requirements

New today, similar wording.

-

SiFive and Ubuntu 22.04 LTS: Linux distribution officially runs on RISC-V CPUs – Research Snipers

The latest edition of the popular Linux distribution Ubuntu from British distributor Canonical now officially runs on processors with SiFive’s RISC-V architecture and StarFive’s single-board computers based on it. For the first time, both companies offer official support for the open source platform.

[...]

At the RISC-V Summit 2021 industry meeting, the company StarFive, co-founded by SiFive, presented the VisionFive V1, a compact single-board computer with the RISC-V processor StarFive JH7100 for AI applications under Linux, which has two processor cores and 8 GB LPDDR4 at 100 × 72 mm. On this system, Canonical and SiFive, and StarFive now offer official support for the free operating system Ubuntu 22.04.1 LTS (“Jammy Jellyfish”) for the first time. Cindy Goldberg, vice president of Silicon Alliance at Canonical, and Thomas Xu, founder and CEO of StarFive, announced in a joint announcement that SiFive, StarFive, and Canonical are working together to advance Ubuntu and Linux on the RISC-V architecture.